Can AI Make a Better Fusion Reactor?

This dance, termed

dynamic voltage and frequency scaling (DVFS), comes about frequently in the processor, termed a procedure-on-chip (SoC), that operates your cellphone and your laptop as perfectly as in the servers that back them. It’s all completed in an work to balance computational general performance with energy intake, anything that is specifically difficult for smartphones. The circuits that orchestrate DVFS strive to make sure a continual clock and a rock-strong voltage level despite the surges in recent, but they are also amongst the most backbreaking to layout.

That is primarily mainly because the clock-generation and voltage-regulation circuits are analog, contrary to virtually every thing else on your smartphone SoC. We have grown accustomed to a near-annually introduction of new processors with significantly additional computational energy, thanks to developments in semiconductor manufacturing. “Porting” a electronic layout from an aged semiconductor system to a new one particular is no picnic, but it can be practically nothing compared to attempting to shift analog circuits to a new system. The analog factors that allow DVFS, particularly a circuit termed a very low-dropout voltage regulator (LDO), do not scale down like electronic circuits do and need to essentially be redesigned from scratch with each new generation.

If we could as a substitute develop LDOs—and potentially other analog circuits—from electronic factors, they would be significantly less complicated to port than any other section of the processor, conserving sizeable layout price and freeing up engineers for other problems that slicing-edge chip layout has in shop. What’s additional, the resulting electronic LDOs could be significantly smaller sized than their analog counterparts and perform far better in specified means. Analysis groups in sector and academia have examined at least a dozen designs above the previous couple a long time, and despite some shortcomings, a commercially handy electronic LDO might before long be in reach.

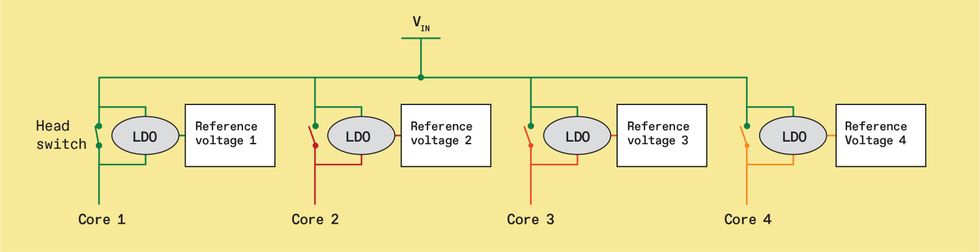

Very low-dropout voltage regulators (LDOs) permit several processor cores on the very same enter voltage rail (VIN) to run at various voltages according to their workloads. In this circumstance, Main one has the best general performance requirement. Its head swap, seriously a team of transistors related in parallel, is closed, bypassing the LDO and straight connecting Main one to VIN, which is provided by an exterior energy administration IC. Cores 2 by way of four, even so, have less demanding workloads. Their LDOs are engaged to offer the cores with voltages that will preserve energy.

The primary analog very low-dropout voltage regulator [remaining] controls voltage by way of a feedback loop. It tries to make the output voltage (VDD) equal to the reference voltage by managing the recent by way of the energy PFET. In the primary electronic layout [ideal], an impartial clock triggers a comparator [triangle] that compares the reference voltage to VDD. The result tells management logic how a lot of energy PFETs to activate.

A Standard Procedure-ON-CHIP for a smartphone is a marvel of integration. On a one sliver of silicon it integrates several CPU cores, a graphics processing device, a electronic sign processor, a neural processing device, an picture sign processor, as perfectly as a modem and other specialized blocks of logic. In a natural way, boosting the clock frequency that drives these logic blocks boosts the fee at which they get their get the job done completed. But to run at a larger frequency, they also need a larger voltage. Devoid of that, transistors are unable to swap on or off right before the future tick of the processor clock. Of training course, a larger frequency and voltage will come at the price of energy intake. So these cores and logic units dynamically adjust their clock frequencies and offer voltages—often ranging from .95 to .forty five volts— based on the balance of power performance and general performance they need to attain for no matter what workload they are assigned—shooting movie, enjoying back a audio file, conveying speech for the duration of a get in touch with, and so on.

Commonly, an exterior energy-administration IC generates several enter voltage (VIN) values for the phone’s SoC. These voltages are delivered to spots of the SoC chip together broad interconnects termed rails. But the variety of connections amongst the energy-administration chip and the SoC is confined. So, several cores on the SoC need to share the very same VIN rail.

But they do not have to all get the very same voltage, thanks to the very low-dropout voltage regulators. LDOs together with focused clock generators permit every core on a shared rail to run at a special offer voltage and clock frequency. The core demanding the best offer voltage determines the shared VIN price. The energy-administration chip sets VIN to this price and this core bypasses the LDO completely by way of transistors termed head switches.

To continue to keep energy intake to a minimum amount, other cores can run at a reduce offer voltage. Program determines what this voltage really should be, and analog LDOs do a pretty great position of giving it. They are compact, very low price to develop, and relatively easy to integrate on a chip, as they do not have to have substantial inductors or capacitors.

But these LDOs can run only in a particular window of voltage. On the superior end, the concentrate on voltage need to be reduce than the variance amongst VIN and the voltage fall across the LDO itself (the eponymous “dropout” voltage). For illustration, if the offer voltage that would be most efficient for the core is .85 V, but VIN is .95 V and the LDO’s dropout voltage is .15 V, that core are unable to use the LDO to reach .85 V and need to get the job done at the .95 V as a substitute, squandering some energy. Similarly, if VIN has presently been set underneath a specified voltage limit, the LDO’s analog factors is not going to get the job done correctly and the circuit are unable to be engaged to cut down the core offer voltage additional.

The principal impediment that has confined use of electronic LDOs so considerably is the slow transient response.

On the other hand, if the preferred voltage falls within the LDO’s window, software program permits the circuit and activates a reference voltage equal to the concentrate on offer voltage.

HOW DOES THE LDO offer the ideal voltage? In the primary analog LDO layout, it can be by usually means of an operational amplifier, feedback, and a specialized energy p-channel subject outcome transistor (PFET). The latter is a transistor that minimizes its recent with expanding voltage to its gate. The gate voltage to this energy PFET is an analog sign coming from the op amp, ranging from volts to VIN. The op amp consistently compares the circuit’s output voltage—the core’s offer voltage, or VDD—to the concentrate on reference voltage. If the LDO’s output voltage falls underneath the reference voltage—as it would when freshly lively logic quickly requires additional current—the op amp minimizes the energy PFET’s gate voltage, expanding recent and lifting VDD towards the reference voltage price. Conversely, if the output voltage rises over the reference voltage—as it would when a core’s logic is less active—then the op amp boosts the transistor’s gate voltage to cut down recent and reduce VDD.

A primary

electronic LDO, on the other hand, is made up of a voltage comparator, management logic, and a variety of parallel energy PFETs. (The LDO also has its personal clock circuit, independent from these utilized by the processor core.) In the electronic LDO, the gate voltages to the energy PFETs are binary values as a substitute of analog, possibly V or VIN.

With every tick of the clock, the comparator measures no matter if the output voltage is underneath or over the concentrate on voltage furnished by the reference source. The comparator output guides the management logic in deciding how a lot of of the energy PFETs to activate. If the LDO’s output is underneath concentrate on, the management logic will activate additional energy PFETs.Their put together recent props up the core’s offer voltage, and that price feeds back to the comparator to continue to keep it on concentrate on. If it overshoots, the comparator alerts to the management logic to swap some of the PFETs off.

NEITHER THE ANALOG nor the electronic LDO is great, of training course. The important gain of an analog layout is that it can respond promptly to transient droops and overshoots in the offer voltage, which is particularly significant when these occasions require steep variations. These transients take place mainly because a core’s need for recent can go up or down considerably in a issue of nanoseconds. In addition to the quickly response, analog LDOs are incredibly great at suppressing versions in VIN that may possibly come in from the other cores on the rails. And, finally, when recent requires are not altering significantly, it controls the output tightly without the need of continually overshooting and undershooting the concentrate on in a way that introduces ripples in VDD.

When a core’s recent requirement variations quickly it can trigger the LDO’s output voltage to overshoot or droop [leading]. Primary electronic LDO designs do not manage this perfectly [base remaining]. On the other hand, a plan termed adaptive sampling with lessened dynamic steadiness [base ideal] can cut down the extent of the voltage tour. It does this by ramping up the LDO’s sample frequency when the droop receives much too substantial, permitting the circuit to respond more quickly.

Supply: S.B. Nasir et al., IEEE Global Strong-Condition Circuits Conference (ISSCC), February 2015, pp. 98–99.

These characteristics have made analog LDOs attractive not just for giving processor cores, but for virtually any circuit demanding a tranquil, continual offer voltage. On the other hand, there are some critical issues that limit the performance of these designs. Very first analog factors are significantly additional complex than electronic logic, demanding lengthy layout situations to implement them in highly developed technological innovation nodes. 2nd, they do not run correctly when VIN is very low, limiting how very low a VDD they can produce to a core. And finally, the dropout voltage of analog LDOs is not as little as designers would like.

Getting these final points alongside one another, analog LDOs supply a confined voltage window at which they can run. That usually means there are missed chances to allow LDOs for energy saving—ones significant more than enough to make a noticeable variance in a smartphone’s battery life.

Electronic LDOs undo a lot of of these weaknesses: With no complex analog factors, they permit designers to tap into a prosperity of resources and other resources for electronic layout. So scaling down the circuit for a new system technological innovation will need significantly less work. Electronic LDOs will also run above a broader voltage variety. At the very low-voltage end, the electronic factors can run at VIN values that are off-limits to analog factors. And in the larger variety, the electronic LDO’s dropout voltage will be smaller sized, resulting in significant core-energy personal savings.

But nothing’s free, and the electronic LDO has some major disadvantages. Most of these occur mainly because the circuit measures and alters its output only at discrete situations, as a substitute of consistently. That usually means the circuit has a comparatively slow response to offer voltage droops and overshoots. It’s also additional delicate to versions in VIN, and it tends to produce little ripples in the output voltage, each of which could degrade a core’s general performance.

Of these, the principal impediment that has confined the use of electronic LDOs so considerably is their slow transient response. Cores practical experience droops and overshoots when the recent they draw abruptly variations in response to a adjust in its workload. The LDO response time to droop occasions is critical to limiting how considerably voltage falls and how very long that issue lasts. Conventional cores include a protection margin to the offer voltage to make sure suitable procedure for the duration of droops. A increased envisioned droop usually means the margin need to be larger sized, degrading the LDO’s power-performance positive aspects. So, dashing up the electronic LDO’s response to droops and overshoots is the key aim of the slicing-edge analysis in this subject.

SOME Recent Advancements have aided pace the circuit’s response to droops and overshoots. A person solution makes use of the electronic LDO’s clock frequency as a management knob to trade steadiness and energy performance for response time.

A reduce frequency increases LDO steadiness, basically mainly because the output will not be altering as typically. It also lowers the LDO’s energy intake, mainly because the transistors that make up the LDO are switching less regularly. But this will come at the price of a slower response to transient recent requires from the processor core. You can see why that would be, if you take into account that significantly of a transient event may possibly take place within a one clock cycle if the frequency is much too very low.

Conversely, a superior LDO clock frequency minimizes the transient response time, mainly because the comparator is sampling the output typically more than enough to adjust the LDO’s output recent before in the transient event. On the other hand, this continuous sampling degrades the steadiness of the output and consumes additional energy.

The gist of this solution is to introduce a clock whose frequency adapts to the scenario, a plan termed adaptive sampling frequency with lessened dynamic steadiness. When voltage droops or overshoots exceed a specified level, the clock frequency boosts to additional promptly cut down the transient outcome. It then slows down to eat less energy and continue to keep the output voltage secure. This trick is reached by including a pair of additional comparators to perception the overshoot and droop situations and induce the clock. In measurements from a take a look at chip employing this method, the VDD droop lessened from 210 to ninety millivolts—a fifty seven % reduction vs . a conventional electronic LDO layout. And the time it took for voltage to settle to a continual point out shrank to one.one microseconds from 5.eight µs, an 81 % enhancement.

An alternate solution for improving the transient response time is to make the electronic LDO a small bit analog. The layout integrates a independent analog-assisted loop that responds instantly to load recent transients. The analog-assisted loop partners the LDO’s output voltage to the LDO’s parallel PFETs by way of a capacitor, building a feedback loop that engages only when there is a steep adjust in output voltage. So, when the output voltage droops, it minimizes the voltage at the activated PFET gates and instantaneously boosts recent to the core to cut down the magnitude of the droop. This kind of an analog-assisted loop has been demonstrated to cut down the droop from three hundred to 106 mV, a 65 % enhancement, and overshoot from eighty to 70 mV (13 %).

An alternate way to make electronic LDOs respond additional rapidly to voltage droops is to include an analog feedback loop to the energy PFET section of the circuit [leading]. When output voltage droops or overshoots, the analog loop engages to prop it up [base], minimizing the extent of the tour.

Supply: M. Huang et al., IEEE Journal of Strong-Condition Circuits, January 2018, pp. 20–34.

Of training course, each of these strategies have their disadvantages. For one particular, neither can seriously match the response time of today’s analog LDOs. In addition, the adaptive sampling frequency method demands two additional comparators and the generation and calibration of reference voltages for droop and overshoot, so the circuit knows when to have interaction the larger frequency. The analog-assisted loop involves some analog factors, minimizing the layout-time profit of an all-electronic procedure.

Developments in business SoC processors might support make electronic LDOs additional thriving, even if they are unable to rather match analog general performance. Nowadays, business SoC processors integrate all-electronic adaptive circuits made to mitigate general performance problems when droops take place. These circuits, for illustration, quickly extend the core’s clock interval to reduce timing glitches. This kind of mitigation strategies could chill out the transient response-time limits, permitting the use of electronic LDOs and boosting processor performance. If that comes about, we can count on additional efficient smartphones and other personal computers, when producing the system of coming up with them a full ton less difficult.